新闻动态/

NEWS

汽车以太网眼图测试的基本原理、测试方法和实际应用案例

2023-12-07 15:50:09

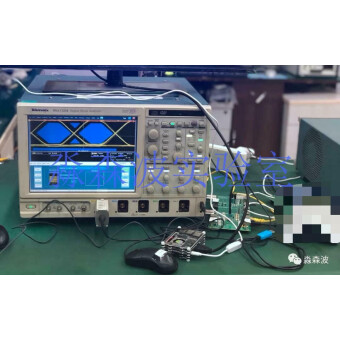

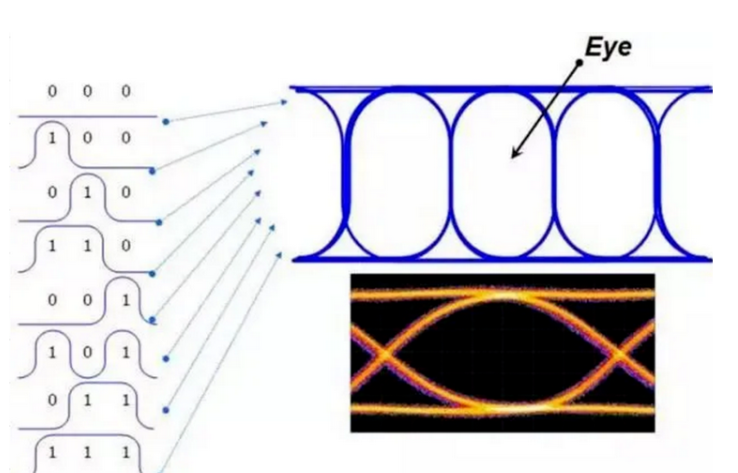

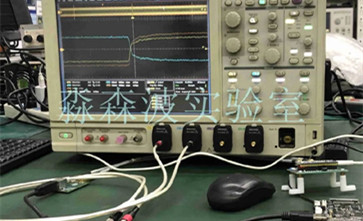

随着汽车电子电气架构的不断演进,以太网技术已成为车载通信和数据交换的重要手段。为了确保汽车以太网通信的可靠性和稳定性,进行眼图测试至关重要。本文将介绍汽车以太网眼图测试的基本原理、测试方法和实际应用案例。一、汽车以太网眼图测试基本原理眼图(Eye Diagram)是一种用于评估数字信号质量的图形表示,可以反映数

汽车以太网眼图测试的基本原理、测试方法和实际应用案例

2023-12-07 15:50:09

随着汽车电子电气架构的不断演进,以太网技术已成为车载通信和数据交换的重要手段。为了确保汽车以太网通信的可靠性和稳定性,进行眼图测试至关重要。本文将介绍汽车以太网眼图测试的基本原理、测试方法和实际应用案例。一、汽车以太网眼图测试基本原理眼图(Eye Diagram)是一种用于评估数字信号质量的图形表示,可以反映数

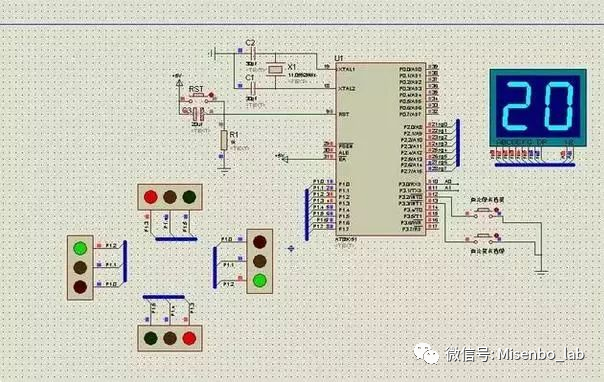

淼森波硬件开放共享实验室-新时代/新趋势/新机会

2023-10-04 17:44:13

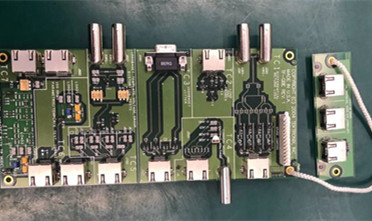

淼森波硬件开放共享实验室-新时代/新趋势/新机会淼森波实验室介绍:硬件共享测试实验室是一个提供硬件设备资源和测试环境的共享平台,主要面向研发团队、创业公司以及个人开发者。它的目的是帮助各类项目在开发和测试过程中节省成本,提高效率。在硬件共享测试实验室中,用户可以租借各种硬件设备,包括但不限于

技术文章/

Technical articles

高速信号有哪些常用的完整性测试方法

2023-12-05 15:59:11

在硬件行业中,对于信号的测试往往能直接反映出一个电子元器件的性能好坏,而对于不同速率的信号,所需要的测试标准也是不一样的。对于低速信号,它的测试标准就会比较低,比如说测量设备的带宽要求,是否需要有源等等都会是非常低的标准,但是对于高速信号,这些条件就会变得非常苛刻,不然测试测量结果就会出现较大偏差。

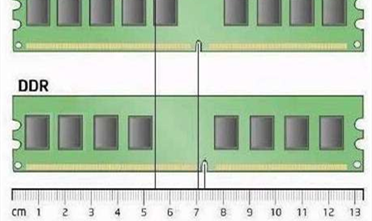

如何区分DDR1,DDR2,DDR3,DDR4还有DDR5?

2023-10-13 10:42:29

01#DDR芯片#以下是芯片DDR1、DDR2、DDR3、DDR4和DDR5的介绍:DDR1(DoubleDataRate)DDR是一种同步动态随机存取存储器,也称为SDRAM(SynchronousDynamicRandomAccessMemory)。它可以在每个时钟周期内进行两次数据传输,提供更高的带宽和更高的性能。DDRSDRAM是DDR内存的一种类

详解10M/100M/1000M以太网接口物理层一致性测试

2023-10-13 10:38:53

以太网的起源与发展1972年Metcalf与他在XeroxPARC的同事们,在研究如何将XeroxAltos工作站与其他XeroxAltos工作站、服务器以及激光打印机相互联网。他们成功地用一个网络实现了2.94Mb/s的数据传输率的互联,并将此网络命名为AltoAloha网络。1973年Metcalf将此延伸至支持其他的计算机类型,并改名为Ethernet。如此

DDR 芯片的 PCB 设计要点

2023-10-11 15:11:16

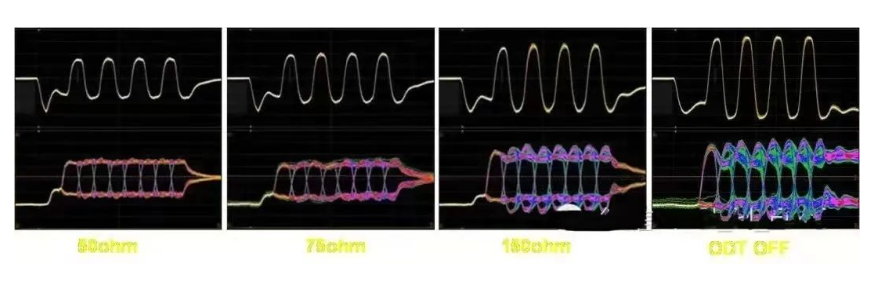

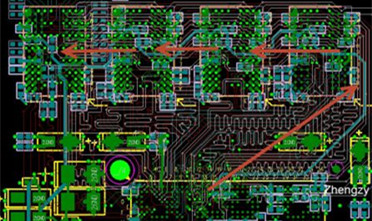

DDR 芯片的 PCB 设计要点1.定义DDR:DoubleDateRate双倍速率同步动态随机存储器。DDR、DDR2、DDR3常用规格:2.阻抗控制要求单端走线控制50欧姆,差分走线控制100欧姆1.地址线(AddressLine)阻抗控制要求:为了减小地址线上的反射和信号干扰,通常要求地

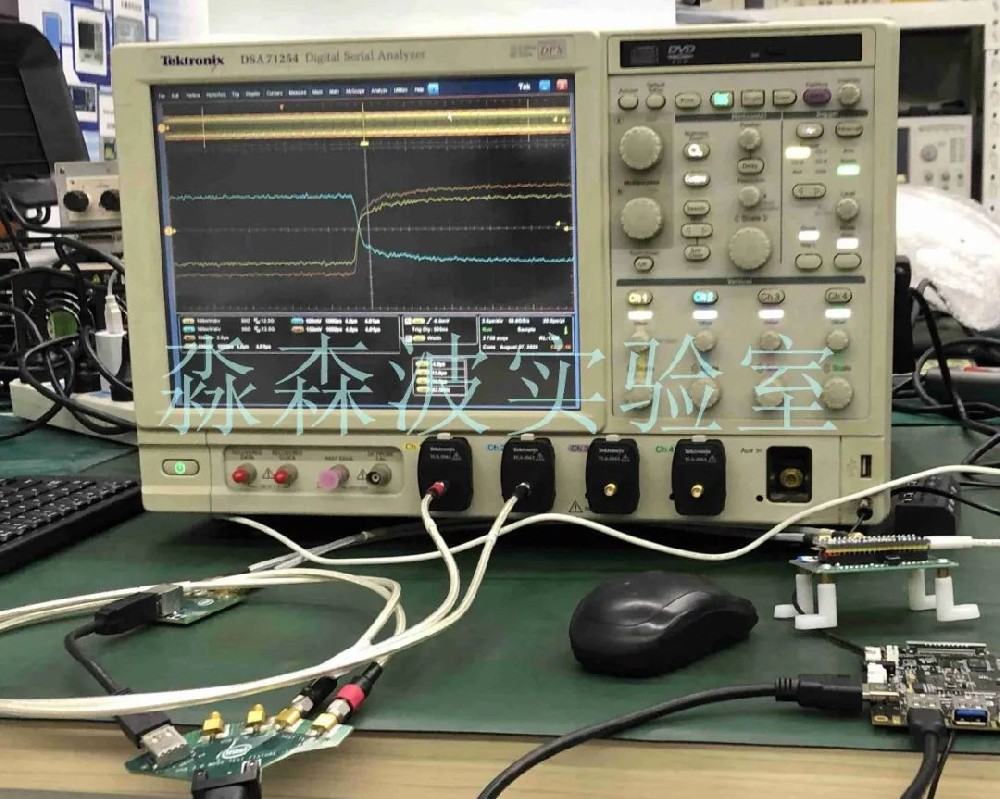

USB3.0一致性测试

2023-10-11 14:56:10

北京淼森波信息技术有限公司USB3.0又称为SuperSpeedUSB,比特率高达5Gbps,相比目前USB2.0的480Mbps的速率,提高了10倍以上。USB3.0和USB2.0相比有着非常本质的区别,USB3.0有两对高速差分线分别进行信号的发送和接收,为全双工工作模式,且使用了多种高速处理技术,如均衡

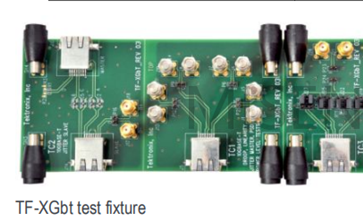

10GBASE-T一致性测试

2023-10-11 14:29:02

10GBASE-T一致性测试10GBASE-T以太网介绍01以太网协议发展至今已历经四代,从最早的10BASE-T到100BASE-T,再到目前市场主流的1000BASE-T,再到方兴未艾的10GBASE-T,每次更新换代都是以10倍的速率在刷新,并且都是向下兼容。10GBASE-T沿用以太网规范,仍然采用RJ-45