MIPI- D -PHY 一致性测试

发布时间:2023-10-11 12:05:42

MIPI- D -PHY 一致性测试

淼森波实验室

MIPI是什么?

MIPI是移动产业处理器接口(MobileIndustry Processor Interface 简称MIPI)的缩写。由英特尔、飞思卡尔、诺基亚、ARM、意法半导体、德州仪器等厂商联盟发起的为移动应用处理器制定的开放标准和一个规范,称为MIPI协议。

MIPI分类?

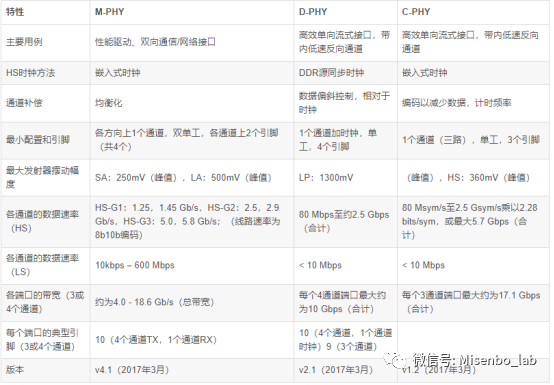

MIPI以速率为主分C-PHY、D-PHY、M-PHY

MIPI- C-PHY,通过带宽受限通道来实现高吞吐量性能,例如将显示器和摄像头连接到应用处理器,例如,安森美(ONSEMI)的FSA660TMX.

MIPI- D-PHY,更常用于智能手机的相机和显示屏,因为它具有灵活、高速、低功耗和低成本的特点

应用于汽车摄像头传感系统、防撞雷达、车内信息娱乐系统和仪表盘显示器。例如,德州仪器(TI)的SNx5DPHY440SS系列

MIPI-M-PHY, 专为需要快速通信通道以支持高分辨率图像、高视频帧速率和大型显示器或存储器的数据密集型应用而设计。这是一款多功能PHY,能够为工程师提供可跨行业平台开发的配置选项和功能,以有效解决多个市场和用例。

MIPI 物理层对比

01

MIPI-CSI&MIPI-DSI接口分类

【测试那点事儿】

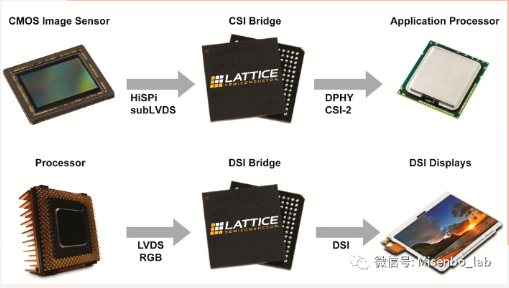

MIPI应用最为成熟的两个接口分别为,MIPI-CSI接口和MIPI-DSI接口,定义如下:

CSI(Camera Serial Interface):一个位于处理器和显示模组之间的高速串行接口;

DSI(Display Serial Interface):一个位于处理器和摄像模组之间的高速串行接口。

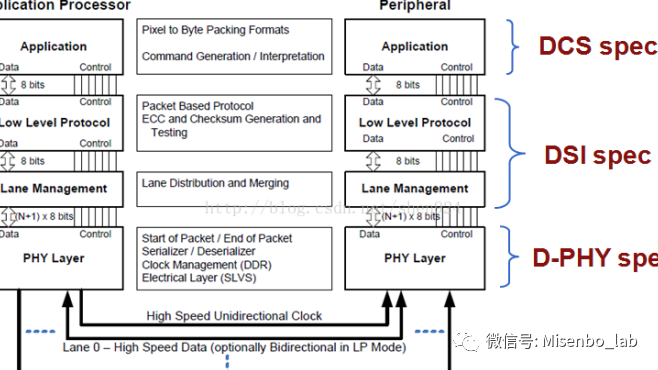

DSI分层结构是什么?

DSI分四层,对应D-PHY、DSI、DCS规范、分层结构如下:

• PHY 定义了传输媒介,输入/输出电路和和时钟和信号机制;

• Lane Management层:发送和收集数据流到每条lane;

• Low Level Protocol层:定义了如何组帧和解析以及错误检测等;

• Application层:描述高层编码和解析数据流。MIPI联盟旨在推进移动应用处理器接口的标准化 。MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风/喇叭接口SLIMbus等

Command和Video模式:

• DSI兼容的外设⽀持Command或Video操作模式,⽤哪个模式由外设的构架决定

• Command模式是指采⽤发送命令和数据到具有显⽰缓存的控制器。主机通过命令间接的控制外设。Command模式采⽤双向接⼝

• Video模式是指从主机传输到外设采⽤时实象素流。这种模式只能以⾼速传输。为减少复杂性和节约成本,只采⽤Video模式的系统可能只 有⼀个单向数据路径

MIPI应用领域:

MIPI标准定义了设计移动设备的行业规范,比如智能手机、平板电脑、便携式电脑和混合设备。MIPI 接口在5G移动设备、互联汽车和物联网解决方案中,具有极其重要的战略作用。具有速度快、传输数据量大、功耗低、抗干扰好的优点越来越受到客户的青睐并在迅速增长。

02

MIPI D- PHY 实测案例

【测试那点事儿】

MIPI D-PHY是一种流行的物理层 (PHY),用于智能手机中的摄像头和显示器,因为它具有灵活性、高速、能效和低成本。由于这些原因,它也被应用于许多其他用例,例如无人机、超大型平板电脑、监控摄像头和工业机器人。D-PHY还大量用于汽车应用,包括摄像头传感系统、防撞雷达、车载信息娱乐和仪表板显示器,并支持专有桥接解决方案。最新版本的规范v3.0将D-PHY标准通道的数据速率翻倍至每秒9 Gbps和11 Gbps的短通道,从而支持最新的超高清显示器及更高版本. 随着数据速率的提升,D-PHY v3.0在连接的接收器侧引入了连续时间线性均衡器 (CTLE),以保持接口的卓越功效。D-PHY v3.0与以前版本的MIPI规范完全兼容。

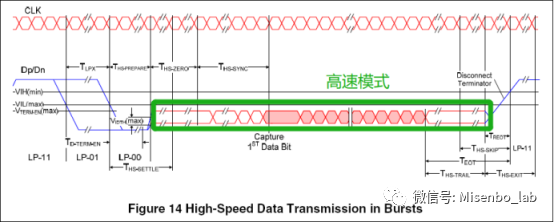

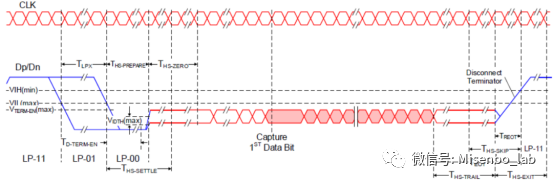

D-PHY和DSI的传输模式:

• 低功耗(Low-Power)信号模式(⽤来控制):10MHz (max)

• ⾼速(High-Speed)信号模式(⽤来⾼速数据传输):80Mbps ~ 1Gbps/Lane

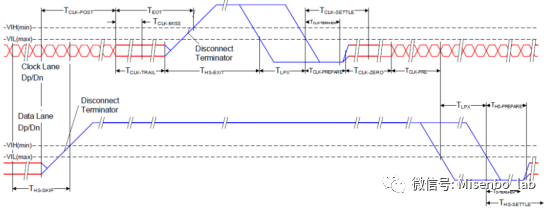

D-PHY的时钟模式:

1、连续模式

2、非连续模式

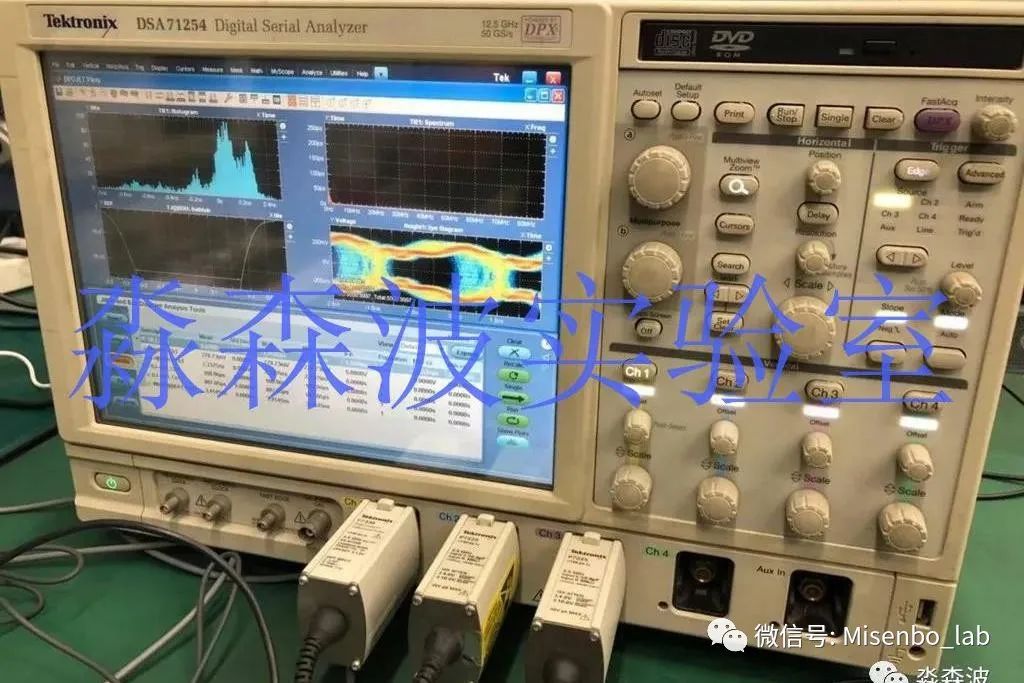

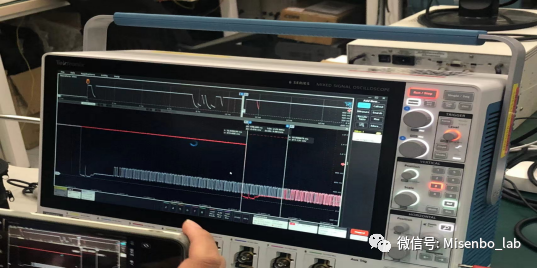

测试仪器

1、 示波器MSO68B

2、 差分探头TDP3500

3、 MIPI 测试软件

测试项目

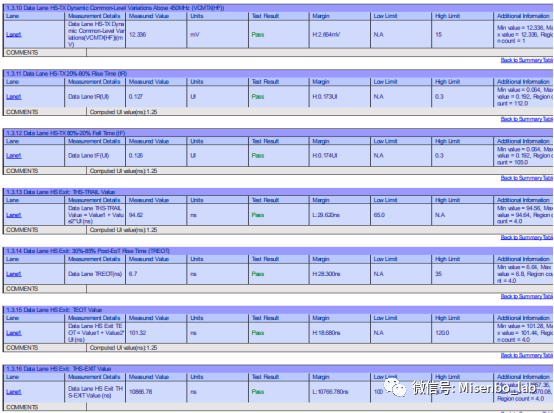

1、Data Lane HS-TX Differential Voltages

2、Data Lane HS-TX Differential Voltage Mismatch

3、Data Lane HS-TX Single-Ended Output High Voltages

4、Data Lane HS-TX Static Common-Mode Voltages

5、Data Lane HS-TX Static Common-Mode Voltage Mismatch ΔV_CMTX(1,0)

6、Data Lane HS-TX Dynamic Common-Level Variations Between 50-450 MHz

7、1.3.10 Data Lane HS-TX Dynamic Common-Level Variations Above 450 MHz

8、Lane HS-TX 20%-80% Rise Time

9、Data Lane HS-TX 80%-20% Fall Time

10、Data Lane HS Entry: T_LPX Value

11、Data Lane HS Entry: T_HS-PREPARE Value

12、Data Lane HS Entry: T_HS-PREPARE + T_HS-ZERO Value

13、Data Lane HS Exit: T_HS-TRAIL Value

14、Data Lane HS Exit: 30%-85% Post-EoT Rise Time T_REOT

15、Data Lane HS Exit: T_EOT Value

16、Data Lane HS Exit: T_HS-EXIT Value

17、HS Entry: T_CLK-PRE Value

18、HS Exit: T_CLK-POST Value

19、HS Clock Rising Edge Alignment to First Payload Bit

20、Data-to-Clock Skew (T_SKEW[TX])

21、Clock Lane HS Clock Instantaneous: UI_INST Value

22、Clock Lane HS Clock Delta UI: (ΔUI)Value

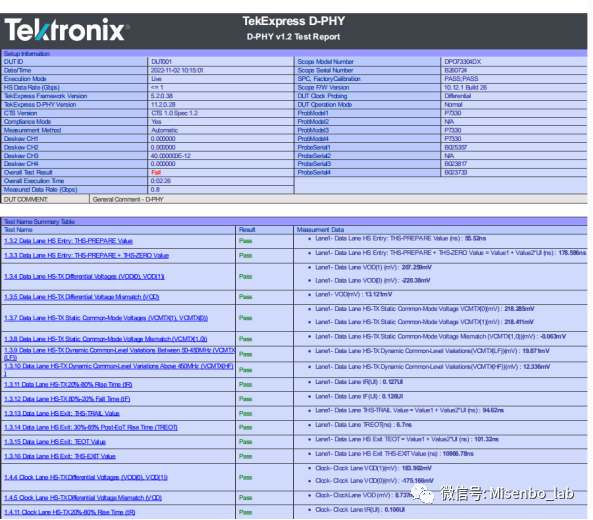

测试报告

END